quartus ii 9.0破解器(附安装教程)

大小:39.8MB

语言:简体中文系统:

类别:其它行业时间:2018-04-19

分类

大小:39.8MB

语言:简体中文系统:

类别:其它行业时间:2018-04-19

quartus ii 9.0是一款适用于芯片(电路)平面布局的PLD/FPGA开发软件,可以为使用者提供提图形界面设计方案。专业性较强,目前小编为大家带来这款软件的9.0版本,小编为大家罗列了该软件的安装教程。该版本还有更多功能也是得到了优化,如果你需要这款软件,那就来下载使用吧!

quartus ii 9.0安装教程

下载Quartus II 9.0正式版

安装Quartus_II_9.0

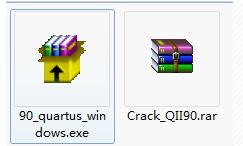

下载90_quartus_windows.exe,这是个自解压文件,有2.4G大小,双击,解压到非系统盘,(这个安装文件比较大,解压到其它盘再安装,否则可能会出现C盘空间不足的现象):接下来默认安装即可。

安装License文件

安装结束后需要安装License,否则只能使用30天,这是重点:

生成License文件

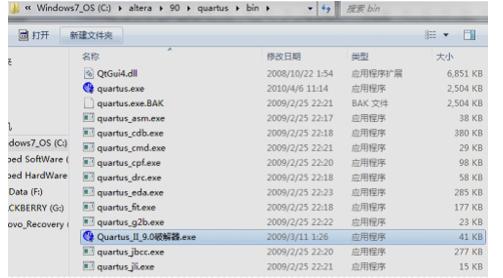

解压上图Crack_QII90.rar到安装目录中(注意:不是自解压目录),我的安装目录是C盘根目录,那么解压的的具体路径是:C:\altera\90\quartus\bin。双击Quartus_II_9.0破解器.exe,(注意:一定要在这个目录运行,否则会提示找不到dll文件),点击“应用补丁”,之后会提示保存“license.DAT”文件,保存至你能找到的地方,我保存至C:\altera。

修改license.DAT

按照“教程系列四-在Win7上安装RVDS.pdf”上修改HOSTID(网卡MAC地址)的方法修改此文件中的HOSTID。

注意一定要保证只有一个网卡,如果有两个,则要禁用那个你不需要的网卡(笔记本一般都有两个网卡)。

安装license文件

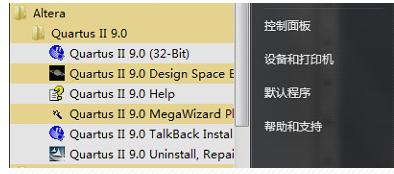

然后打开“Quartus II 9.0 (32-Bit)”,点击菜单栏中Tools->License Setup

点击右上角的。。。。,选中刚才生成的license.DAT文件,然后点击OK即可。

安装破解完成

相关介绍

QuartusIIdesign是最高级和复杂的,用于system-on-a-programmable-chip(SOPC)的设计环境。QuartusIIdesign提供完善的timingclosure和LogicLock™基于块的设计流程。QuartusIIdesign是唯一一个包括以timingclosure和基于块的设计流为基本特征的programmablelogicdevice(PLD)的软件。QuartusII设计软件改进了性能、提升了功能性、解决了潜在的设计延迟等,在工业领域率先提供FPGA与mask-programmeddevices开发的统一工作流程。

Quartus II是Altera公司的综合性PLD/FPGA开发软件,原理图、VHDL、VerilogHDL以及AHDL(Altera Hardware 支持Description Language)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

功能

Quartus II可以在Windows、Linux以及Unix上使用,除了可以使用Tcl脚本完成设计流程外,提供了完善的用户图形界面设计方式。具有运行速度快,界面统一,功能集中,易学易用等特点。

Quartus II支持Altera的IP核,包含了LPM/MegaFunction宏功能模块库,使用户可以充分利用成熟的模块,简化了设计的复杂性、加快了设计速度。对第三方EDA工具的良好支持也使用户可以在设计流程的各个阶段使用熟悉的第三方EDA工具。

此外,Quartus II 通过和DSP Builder工具与Matlab/Simulink相结合,可以方便地实现各种DSP应用系统;支持Altera的片上可编程系统(SOPC)开发,集系统级设计、嵌入式软件开发、可编程逻辑设计于一体,是一种综合性的开发平台。

Maxplus II 作为Altera的上一代PLD设计软件,由于其出色的易用性而得到了广泛的应用。目前Altera已经停止了对Maxplus II 的更新支持,Quartus II 与之相比不仅仅是支持器件类型的丰富和图形界面的改变。Altera在Quartus II 中包含了许多诸如SignalTap II、Chip Editor和RTL Viewer的设计辅助工具,集成了SOPC和HardCopy设计流程,并且继承了Maxplus II 友好的图形界面及简便的使用方法。

Altera Quartus II 作为一种可编程逻辑的设计环境, 由于其强大的设计能力和直观易用的接口,越来越受到数字系统设计者的欢迎。

Quartus II软件与ISE软件分别是干什么用的?

Quartus II 是Altera公司的综合性PLD/FPGA开发软件,原理图、VHDL、VerilogHDL以及AHDL(Altera Hardware 支持Description Language)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

ISE是使用XILINX的FPGA的必备的设计工具。目前官方提供下载的最新版本是14.4。它可以完成FPGA开发的全部流程,包括设计输入、仿真、综合、布局布线、生成BIT文件、配置以及在线调试等,功能非常强大。ISE除了功能完整,使用方便外,它的设计性能也非常好,以ISE 9.x来说,其设计性能比其他解决方案平均快30%,它集成的时序收敛流程整合了增强性物理综合优化,提供最佳的时钟布局、更好的封装和时序收敛映射,从而获得更高的设计性能。

Quartus II设计套装的其他特性

· DSP Builder 12.0新的数字信号处理(DSP)支持——通过系统控制台,与MATLAB的DDR存储器进行通信,并具有新的浮点功能,提高了设计效能,以及DSP效率。

· 经过改进的视频和图像处理(VIP)套装以及视频接口IP——通过具有边缘自适应算法的Scaler II MegaCore功能以及新的Avalon-Streaming (Avalon-ST)视频监视和跟踪系统IP内核,简化了视频处理应用的开发。

· 增强收发器设计和验证——更新了Arria V FPGA的收发器工具包支持,进一步提高收发器数据速率(对于Stratix V FPGA,高达14.1 Gbps)。

猜您喜欢